INSTITUTO POLITÉCNICO NACIONAL

---

---

ESCUELA SUPERIOR DE CÓMPUTO

SECCIÓN DE ESTUDIOS DE POSGRADO E

INVESTIGACIÓN

ARQUITECTURA DE HARDWARE BASADA EN

MATRICES SISTÓLICAS PARA COMPRESIÓN DE DATOS

SIN PÉRDIDA

T E S I S

QUE PARA OBTENER EL TÍTULO DE:

MAESTRÍA EN CIENCIAS EN INGENIERÍA EN

SISTEMAS COMPUTACIONALES MÓVILES

PRESENTA:

ING. EDUARDO IvÁN MEJÍA BELLO

DIRECTORES DE TESIS:

M. EN C. ERIKA HERNÁNDEZ RUBIO

DR. GELACIO CASTILLO CABRERA

INSTITUTO POLITÉCNICO NACIONAL

SECRETARIA DE INVESTIGACIÓN Y POSGRADO

Dirección de Posgrado

SIP-13

REP 2017

ACTA DE REGISTRO DE TEMA DE TESIS

Y DESIGNACIÓN DE DIRECTOR DE TESIS

Ciudad de México, a 30 de abril del 2025

El Colegio de Profesores de Posgrado de Escuela Superior de Cómputo (Unidad Académica) en su Sesión

Ordinaria No. 4 celebrada el día 11 del mes abril de 2025 conoció la solicitud presentada por el (la) alumno (a):

|                   |       |                   |       |             |              |

|-------------------|-------|-------------------|-------|-------------|--------------|

| Apellido Paterno: | Mejía | Apellido Materno: | Bello | Nombre (s): | Eduardo Iván |

|-------------------|-------|-------------------|-------|-------------|--------------|

Número de boleta: B | 2 | 3 | 0 | 6 | 3 | 9

del Programa Académico de Posgrado: Maestría en Ciencias en Sistemas Computacionales Móviles

Referente al registro de su tema de tesis

1.- Se acordó aprobar el tema de tesis:

Arquitectura de hardware basada en matrices sistólicas para compresión de datos sin pérdida

Objetivo general del trabajo de tesis:

Diseñar e implementar una arquitectura de hardware especializada en compresión de texto sin pérdida, basada en LZ77, empleando matrices sistólicas.

2.- Se designa como Directores de Tesis a los profesores:

Director: M. en C. Erika Hernández Rubio

Director: Dr. Gelacio Castillo Cabrera

No aplica:

3.- El Trabajo de investigación base para el desarrollo de la tesis será elaborado por el alumno en:

SEPI-ESCOM

que cuenta con los recursos e infraestructura necesarios.

4.- El interesado deberá asistir a los seminarios desarrollados en el área de adscripción del trabajo desde la fecha en que se suscribe la presente, hasta la aprobación de la versión completa de la tesis por parte de la Comisión Revisora correspondiente.

Director(a) de Tesis

M. en C. Erika Hernández Rubio

Alumno

Mejía Bello Eduardo Iván

Director de Tesis (en su caso)

Presidente del Colegio

M. en C. Iván Giovanny Mossb. García

S.E.P.

INSTITUTO POLITÉCNICO NACIONAL

ESCUELA SUPERIOR DE COMPUTO

INSTITUTO POLITÉCNICO NACIONAL

SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

Dirección de Posgrado

SIP-14

REP 2017

ACTA DE REVISIÓN DE TESIS

En la Ciudad de **México** siendo las **12:00** horas del día **25** del mes de **junio**

del **2025** se reunieron los miembros de la Comisión Revisora de la Tesis, designada por el Colegio de Profesores de Posgrado de: **Escuela Superior de Cómputo** para examinar la tesis titulada:

**Arquitectura de hardware basada en matrices sistólicas para compresión de datos sin pérdida** del (la) alumno (a):

|                   |              |                   |              |             |                     |

|-------------------|--------------|-------------------|--------------|-------------|---------------------|

| Apellido Paterno: | <b>Mejía</b> | Apellido Materno: | <b>Bello</b> | Nombre (s): | <b>Eduardo Iván</b> |

|-------------------|--------------|-------------------|--------------|-------------|---------------------|

Número de boleta: **B 2 3 0 6 3 9**

Alumno del Programa Académico de Posgrado:

**Maestría en Ciencias en Sistemas Computacionales Móviles**

Una vez que se realizó un análisis de similitud de texto, utilizando el software antiplagio, se encontró que el trabajo de tesis tiene 6 % de similitud. **Se adjunta reporte de software utilizado.**

Después que esta Comisión revisó exhaustivamente el contenido, estructura, intención y ubicación de los textos de la tesis identificados como coincidentes con otros documentos, concluyó que en el presente trabajo **SI  NO  SE CONSTITUYE UN POSIBLE PLAGIO.**

**JUSTIFICACIÓN DE LA CONCLUSIÓN:** *(Por ejemplo, el % de similitud se localiza en metodologías adecuadamente referidas a fuente original)*

**Por nombres de instituciones, referencias, nombres de profesores**

Finalmente y posterior a la lectura, revisión individual, así como el análisis e intercambio de opiniones, los miembros de la Comisión manifestaron **APROBAR  SUSPENDER  NO APROBAR**  la tesis por **UNANIMIDAD  o MAYORÍA**  en virtud de los motivos siguientes:

*Se leyó el alcance de los objetivos. Se realizaron las pruebas para validar la arquitectura propuesta.*

M. en C. Erika Hernández Rubio

Director de Tesis

Nombre completo y firma

2º Director de Tesis (en su caso)

Nombre completo y firma

COMISIÓN REVISORA DE TESIS

Dra. Miriam Pescador Rojas

Nombre completo y firma

Nombre completo y firma

M. en C. Rodolfo Romero Herrera

Nombre completo y firma

**INSTITUTO POLITÉCNICO NACIONAL**

**SECRETARÍA DE INVESTIGACIÓN Y POSGRADO**

**CARTA DE AUTORIZACIÓN DE USO DE OBRA PARA DIFUSIÓN**

En la Ciudad de México el día 06 del mes de julio del año 2025, el que suscribe Eduardo Iván Mejía Bello, alumno del programa Maestría en Ciencias en Sistemas Computacionales Móviles con número de registro B230639, adscrito(a) a Escuela Superior de Cómputo manifiesta que es autor(a) intelectual del presente trabajo de tesis bajo la dirección de M. en C. Erika Hernández Rubio y el Dr. Gelacio Castillo Cabrera y cede los derechos del trabajo intitulado: Arquitectura de hardware basada en matrices sistólicas para compresión de datos sin pérdida, al Instituto Politécnico Nacional, para su difusión con fines académicos y de investigación.

Los usuarios de la información no deben reproducir el contenido textual, gráficas o datos del trabajo sin el permiso expresado del autor y/o director(es). Este puede ser obtenido escribiendo a las siguiente(s) dirección(es) de correo. [emejia010@gmail.com](mailto:emejia010@gmail.com), [emejia0900@alumno.ipn.mx](mailto:emejia0900@alumno.ipn.mx). Si el permiso se otorga, al usuario deberá dar agradecimiento correspondiente y citar la fuente de este.

Nombre completo y firma autógrafa del (de la)

estudiante

*A mi esposa y a mi gata, por darme claridad en los días difíciles y recordarme que distraerme también es importante.*

# Agradecimientos

Este trabajo representa un logro en mi formación académica y personal, y no habría sido posible sin el respaldo de personas cuya presencia ha sido determinante en este camino. Agradezco profundamente al Dr. Gelacio Castillo Cabrera, director de esta tesis, por su orientación constante, por inspirarme a comprender a fondo el funcionamiento interno de los sistemas de cómputo y por fomentar en mí la iniciativa de asumir desafíos comparables a los que enfrentan grandes industrias. Su guía encendió en mí una curiosidad que se convirtió en el motor de esta investigación.

A la M. en C. Erika Hernández Rubio, codirectora de este trabajo, le agradezco sinceramente por su apoyo durante las etapas iniciales, cuando aún no sabía cómo abordar adecuadamente el problema, ni qué ruta debía seguir. Su claridad y firmeza fueron clave para enfocar el esfuerzo de forma efectiva.

A mis padres, por su presencia constante, por escuchar mis ideas, por alentar mis proyectos, y por brindarme enseñanzas y momentos que atesoro profundamente. A mi hermana, por preocuparse por mi bienestar, por impulsarme a ser mejor cada día y por ser una fuente incondicional de apoyo emocional.

Finalmente, a mi esposa, por acompañarme con paciencia y entrega, por escuchar incluso lo que parecía insignificante, y por construir conmigo un camino en el que ambos podamos crecer, comprendernos y sostenernos mutuamente. Su presencia ha sido un pilar firme en el desarrollo de esta investigación y en la consolidación de este logro.

# Resumen

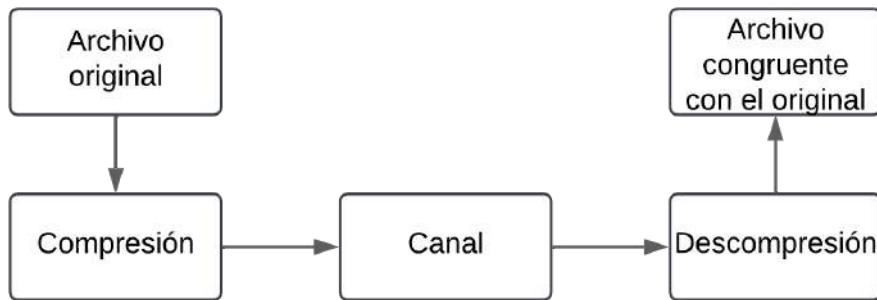

Se aborda el diseño de una arquitectura de hardware especializada en compresión de datos sin pérdida, para su futura implementación como un procesador adicional en diversos sistemas. Se realiza el diseño con los principios conocidos como matrices sistólicas. Con ello se disminuye el uso de recursos en el procesador principal realizando la tarea de compresión, un proceso crítico en la vida diaria. Considerando la gran cantidad de dispositivos y software a nivel mundial que realizan este proceso de una u otra forma, al grado que se ha vuelto transparente para el usuario, pero, sigue siendo de suma importancia tanto en el almacenamiento como en la transmisión de información. Con ello, debido al constante incremento de generación de datos y los recursos limitados para poder procesarlos, el tráfico de las redes y la amplia utilización del almacenamiento de datos digitales que se exige en la actualidad; la implementación de algoritmos de compresión de datos en hardware cobra relevancia. El documento revisa diversas técnicas de compresión sin pérdidas, desde su fundamento matemático, como los códigos Huffman, el código aritmético y los algoritmos de Lempel-Ziv (LZ). Se explora el conocimiento necesario para diseñar una implementación basada en el algoritmo de ventana deslizante, tomando en cuenta aspectos técnicos y mejoras que se pueden llevar a cabo. Además, se realiza una prueba de concepto del diseño desarrollado sobre un FPGA, aprovechando su capacidad para realizar múltiples funciones digitales mediante la configuración de bloques lógicos programables y sus interconexiones. La estructura del documento comprende secciones como introducción, planteamiento del problema, justificación, objetivos, antecedentes, metodología, estado del arte, diseño, construcción y pruebas.

# Abstract

This work presents the design of a hardware architecture specialized in lossless data compression, intended for future integration as an auxiliary processor within various systems. The design is based on systolic array principles, enabling the offloading of compression tasks from the main processor. This approach is especially relevant given that compression is a critical process in daily computing, across devices and software worldwide, to the extent that it has become transparent to the end-user. Nonetheless, compression remains essential for both data storage and transmission.

Due to the ever-increasing generation of data and the limited resources available to process it, as well as the demands on network traffic and digital storage, the implementation of data compression algorithms in hardware is of growing importance. This document reviews various lossless compression techniques, including their mathematical foundations such as Huffman coding, arithmetic coding, and the Lempel-Ziv (LZ) family of algorithms. A detailed analysis of sliding window-based implementations is presented, considering technical trade-offs and optimization strategies.

A proof of concept of the proposed architecture was developed and tested on an FPGA, leveraging its reconfigurable logic blocks and interconnects to perform specialized digital functions. The structure of this thesis includes sections on introduction, problem statement, justification, objectives, background, methodology, state of the art, design, implementation, and testing.

# Índice general

|          |                                                              |           |

|----------|--------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introducción</b>                                          | <b>1</b>  |

| 1.1      | Planteamiento del problema . . . . .                         | 2         |

| 1.1.1    | Pregunta de investigación . . . . .                          | 3         |

| 1.1.2    | Propuesta de solución . . . . .                              | 3         |

| 1.2      | Objetivos . . . . .                                          | 5         |

| 1.2.1    | Objetivo general . . . . .                                   | 5         |

| 1.2.2    | Objetivos específicos . . . . .                              | 5         |

| 1.3      | Justificación . . . . .                                      | 5         |

| 1.4      | Metodología . . . . .                                        | 7         |

| 1.5      | Cronograma . . . . .                                         | 8         |

| 1.6      | Estado del arte . . . . .                                    | 8         |

| 1.6.1    | Compresión en dispositivos móviles . . . . .                 | 13        |

| <b>2</b> | <b>Marco teórico</b>                                         | <b>16</b> |

| 2.1      | Fundamentos matemáticos . . . . .                            | 17        |

| 2.1.1    | Teoría de la información . . . . .                           | 17        |

| 2.1.2    | Códigos prefijos . . . . .                                   | 19        |

| 2.1.3    | Métodos estadísticos . . . . .                               | 20        |

| 2.2      | Métodos de diccionario . . . . .                             | 22        |

| 2.2.1    | Algoritmos de codificación LZ . . . . .                      | 23        |

| 2.2.2    | Un ejemplo de compresión . . . . .                           | 24        |

| 2.3      | Computación en paralelo . . . . .                            | 25        |

| 2.3.1    | Importancia del paralelismo . . . . .                        | 25        |

| 2.3.2    | Tipos de paralelismo . . . . .                               | 25        |

| 2.3.3    | Ventajas y retos . . . . .                                   | 26        |

| 2.3.4    | Paralelismo y la taxonomía de Flynn . . . . .                | 26        |

| 2.3.5    | Importancia de la taxonomía de Flynn . . . . .               | 26        |

| 2.3.6    | Aplicaciones relevantes . . . . .                            | 27        |

| 2.3.7    | Aplicación en arquitecturas de compresión . . . . .          | 27        |

| 2.4      | Matrices sistólicas en la arquitectura de hardware . . . . . | 27        |

| 2.4.1    | Método seleccionado . . . . .                                | 29        |

| <b>3</b> | <b>Análisis</b>                                              | <b>30</b> |

| 3.1      | Algoritmo LZ77 a detalle . . . . .                           | 30        |

| 3.1.1    | Complejidad computacional del algoritmo LZ77 . . . . .       | 32        |

|          |                                                                                      |           |

|----------|--------------------------------------------------------------------------------------|-----------|

| 3.1.2    | Impacto en el diseño de hardware . . . . .                                           | 33        |

| 3.2      | Descripción del hardware empleado . . . . .                                          | 33        |

| 3.2.1    | Características de la tarjeta AX7A200 . . . . .                                      | 34        |

| 3.2.2    | Especificaciones técnicas del FPGA Artix-7 XC7A200T . . . . .                        | 34        |

| 3.2.3    | Consumo energético y rendimiento térmico . . . . .                                   | 35        |

| 3.2.4    | Velocidad de operación y latencia . . . . .                                          | 35        |

| 3.2.5    | Escalabilidad y aplicaciones . . . . .                                               | 35        |

| 3.3      | Desarrollo de modelo general . . . . .                                               | 36        |

| 3.3.1    | Definición de casos de prueba . . . . .                                              | 37        |

| 3.4      | Especificación de requerimientos del sistema . . . . .                               | 39        |

| 3.4.1    | Requerimientos funcionales . . . . .                                                 | 39        |

| 3.4.2    | Requerimientos no funcionales . . . . .                                              | 39        |

| 3.5      | Propuesta: Compresor con ventana deslizante . . . . .                                | 40        |

| 3.5.1    | Ejemplo de comparaciones y salidas . . . . .                                         | 42        |

| 3.5.2    | Diccionario dinámico . . . . .                                                       | 43        |

| 3.6      | Descripción del algoritmo de compresión en hardware . . . . .                        | 46        |

| 3.6.1    | Módulos y funcionalidades . . . . .                                                  | 47        |

| 3.6.2    | Maquina de estados . . . . .                                                         | 47        |

| 3.6.3    | Optimizaciones y rendimiento . . . . .                                               | 47        |

| 3.7      | Descripción del algoritmo de descompresión en hardware . . . . .                     | 48        |

| 3.7.1    | Máquina de estados . . . . .                                                         | 48        |

| 3.7.2    | Implementación y funcionalidad . . . . .                                             | 49        |

| 3.8      | Construcción de la lista de funcionalidades . . . . .                                | 49        |

| 3.8.1    | Preprocesamiento de datos . . . . .                                                  | 50        |

| 3.8.2    | Gestión de condiciones de búsqueda . . . . .                                         | 51        |

| 3.8.3    | Búsqueda de coincidencias . . . . .                                                  | 51        |

| 3.8.4    | Bloque de decisión de coincidencias . . . . .                                        | 51        |

| 3.8.5    | Generador de código comprimido . . . . .                                             | 51        |

| 3.9      | Planeación por funcionalidades . . . . .                                             | 51        |

| 3.9.1    | Diseño y desarrollo de módulos (Septiembre - Diciembre) . . . . .                    | 52        |

| 3.9.2    | Integración y validación (Enero - Junio) . . . . .                                   | 52        |

| <b>4</b> | <b>Diseño</b>                                                                        | <b>53</b> |

| 4.1      | Diseño de matriz sistólica . . . . .                                                 | 53        |

| 4.1.1    | Elementos de procesamiento . . . . .                                                 | 55        |

| 4.2      | Módulo de preprocesamiento de datos . . . . .                                        | 57        |

| 4.3      | Módulo de gestión de condiciones de búsqueda . . . . .                               | 57        |

| 4.4      | Módulo de búsqueda de coincidencias . . . . .                                        | 59        |

| 4.4.1    | Operaciones de los ePs . . . . .                                                     | 60        |

| 4.5      | Módulo de decisión de coincidencias . . . . .                                        | 61        |

| 4.6      | Módulo generador de código comprimido . . . . .                                      | 62        |

| 4.7      | Especificaciones de entradas y salidas para los módulos de la arquitectura . . . . . | 63        |

| <b>5</b> | <b>Construcción</b>                                                                  | <b>64</b> |

| 5.1      | Módulo de preprocesamiento de datos . . . . .                                        | 64        |

|          |                                                                                    |           |

|----------|------------------------------------------------------------------------------------|-----------|

| 5.2      | Módulo de gestión de condiciones de búsqueda . . . . .                             | 65        |

| 5.2.1    | Estructura del módulo e implementación en verilog . . . . .                        | 65        |

| 5.3      | Módulo de búsqueda de coincidencias . . . . .                                      | 65        |

| 5.3.1    | Especificaciones . . . . .                                                         | 66        |

| 5.4      | Modulo de decisión de coincidencias . . . . .                                      | 66        |

| 5.5      | Generador de código comprimido . . . . .                                           | 67        |

| <b>6</b> | <b>Pruebas</b>                                                                     | <b>68</b> |

| 6.1      | Conjunto de datos . . . . .                                                        | 68        |

| 6.2      | Dispositivos a comparar . . . . .                                                  | 70        |

| 6.2.1    | Consideraciones sobre el tiempo medido en dispositivos Android . . . . .           | 70        |

| 6.3      | Pruebas en simulación . . . . .                                                    | 71        |

| 6.3.1    | Conversión de frecuencia a período . . . . .                                       | 72        |

| 6.3.2    | Comparativa con Calgary Corpus . . . . .                                           | 72        |

| 6.3.3    | Comparativa con Canterbury Corpus . . . . .                                        | 73        |

| 6.3.4    | Comparativa con Silesia Corpus . . . . .                                           | 75        |

| 6.4      | Pruebas en tarjeta de desarrollo . . . . .                                         | 76        |

| 6.4.1    | Configuración y uso de relojes diferenciales en FPGA . . . . .                     | 76        |

| 6.4.2    | Tarjeta SD . . . . .                                                               | 77        |

| 6.4.3    | Implementación del acceso al sistema de archivos FAT y FAT16 . . . . .             | 80        |

| 6.4.4    | Depuración de arquitectura mediante el Analizador Lógico Integrado (ILA) . . . . . | 83        |

| 6.4.5    | Comparativa con Calgary Corpus . . . . .                                           | 84        |

| 6.4.6    | Comparativa con Canterbury Corpus . . . . .                                        | 85        |

| 6.4.7    | Comparativa con Silesia Corpus . . . . .                                           | 86        |

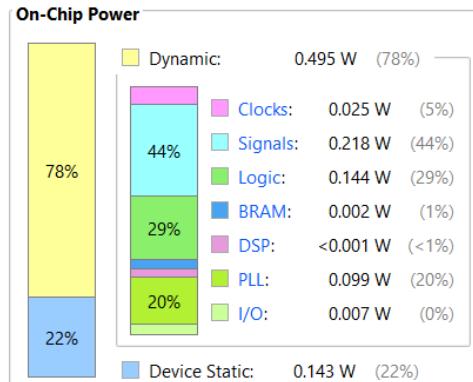

| 6.5      | Consumo energético . . . . .                                                       | 88        |

| 6.5.1    | Análisis del consumo de potencia . . . . .                                         | 88        |

| 6.5.2    | Distribución de potencia por componente en chip . . . . .                          | 88        |

| 6.5.3    | Distribución por dominio de alimentación . . . . .                                 | 88        |

| 6.5.4    | Distribución jerárquica del consumo en el diseño . . . . .                         | 89        |

| 6.5.5    | Análisis térmico de la arquitectura . . . . .                                      | 89        |

| 6.5.6    | Medición física . . . . .                                                          | 90        |

| 6.5.7    | Análisis comparativo del consumo energético . . . . .                              | 90        |

| 6.5.8    | Análisis del tiempo empleado . . . . .                                             | 91        |

| 6.5.9    | Discusión de resultados . . . . .                                                  | 93        |

| <b>7</b> | <b>Conclusión</b>                                                                  | <b>94</b> |

| 7.1      | Respuesta a la pregunta de investigación . . . . .                                 | 95        |

| 7.2      | Trabajo a Futuro . . . . .                                                         | 96        |

| <b>A</b> | <b>Anexo</b>                                                                       | <b>98</b> |

| A.1      | La Desigualdad de Kraft-McMillan . . . . .                                         | 98        |

| A.2      | Código fuente . . . . .                                                            | 99        |

| A.3      | Esquemáticos de diseño de arquitectura . . . . .                                   | 102       |

# Índice de figuras

|      |                                                                                            |    |

|------|--------------------------------------------------------------------------------------------|----|

| 1.1  | Metodología basada en funciones, basado en (18). . . . .                                   | 7  |

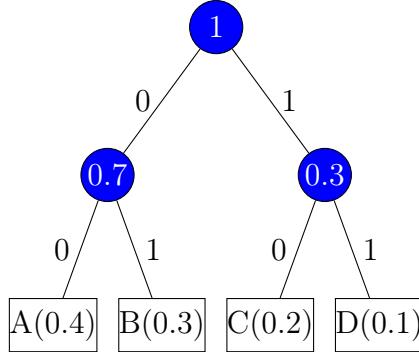

| 2.1  | Árbol de codificación Shannon-Fano, elaboración propia. . . . .                            | 22 |

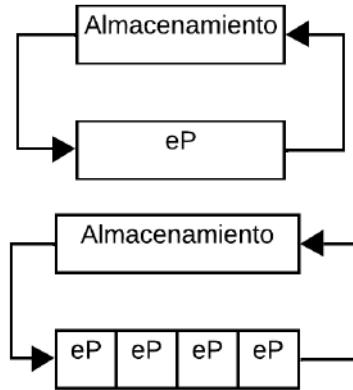

| 2.2  | Diagrama de matriz sistólica, basado en [1]. . . . .                                       | 28 |

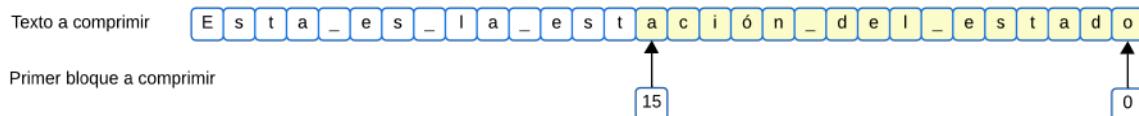

| 3.1  | Ejemplo de ventana deslizante, elaboración propia. . . . .                                 | 30 |

| 3.2  | FPGA utilizada, tomado de [2] . . . . .                                                    | 34 |

| 3.3  | Diagrama de bloques básico de compresión, elaboración propia. . . . .                      | 36 |

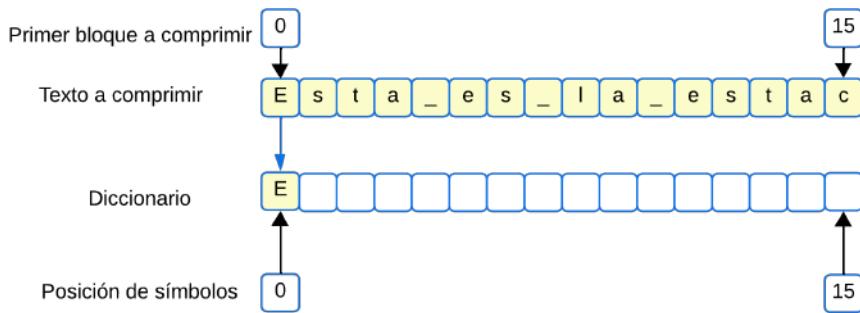

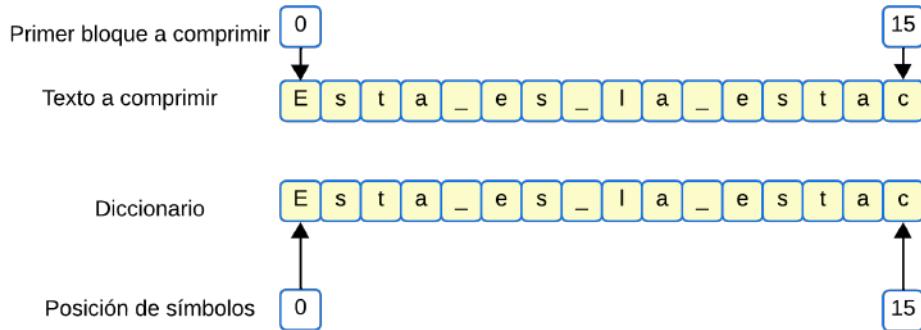

| 3.4  | Texto de ejemplo, elaboración propia. . . . .                                              | 41 |

| 3.5  | Diccionario propuesto, elaboración propia. . . . .                                         | 41 |

| 3.6  | Diccionario con posiciones corregidas, elaboración propia. . . . .                         | 42 |

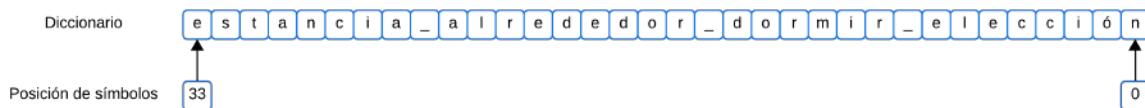

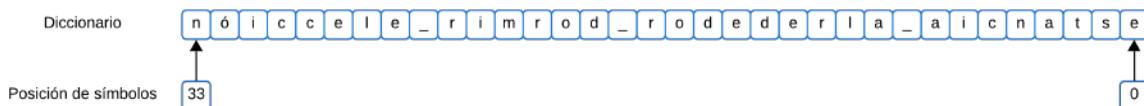

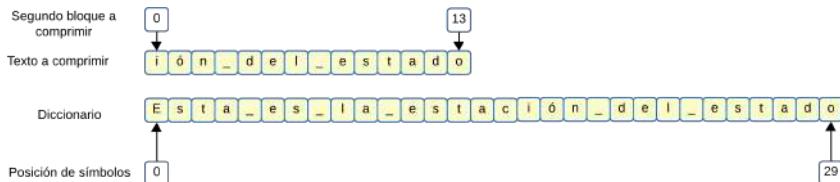

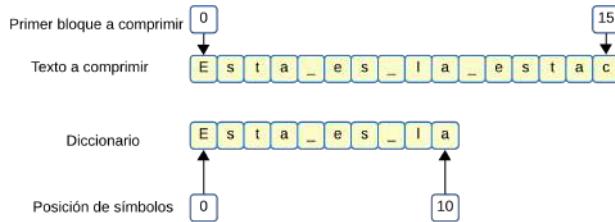

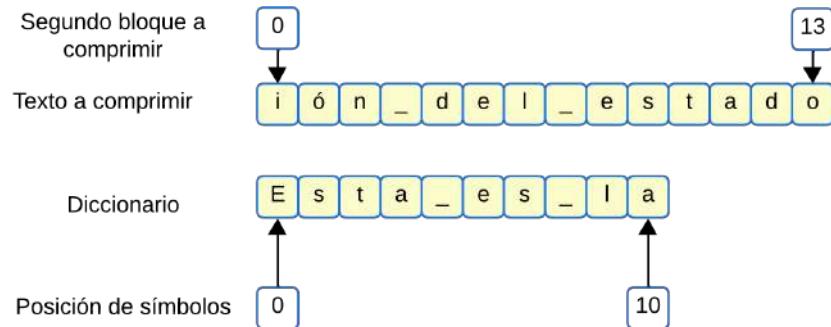

| 3.7  | Diccionario dinámico propuesto, elaboración propia. . . . .                                | 44 |

| 3.8  | Diccionario dinámico bloque 1, elaboración propia. . . . .                                 | 44 |

| 3.9  | Diccionario dinámico bloque 2, elaboración propia. . . . .                                 | 44 |

| 3.10 | Diccionario dinámico pequeño con bloque 1, elaboración propia. . . . .                     | 46 |

| 3.11 | Diccionario dinámico pequeño con bloque 2, elaboración propia. . . . .                     | 46 |

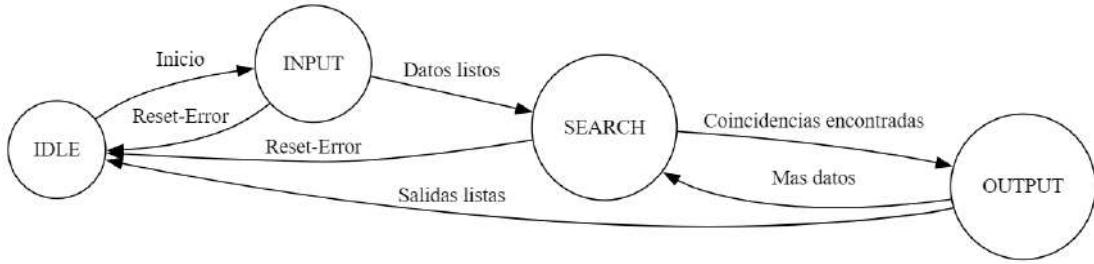

| 3.12 | Maquina de estados base de compresor, elaboración propia. . . . .                          | 48 |

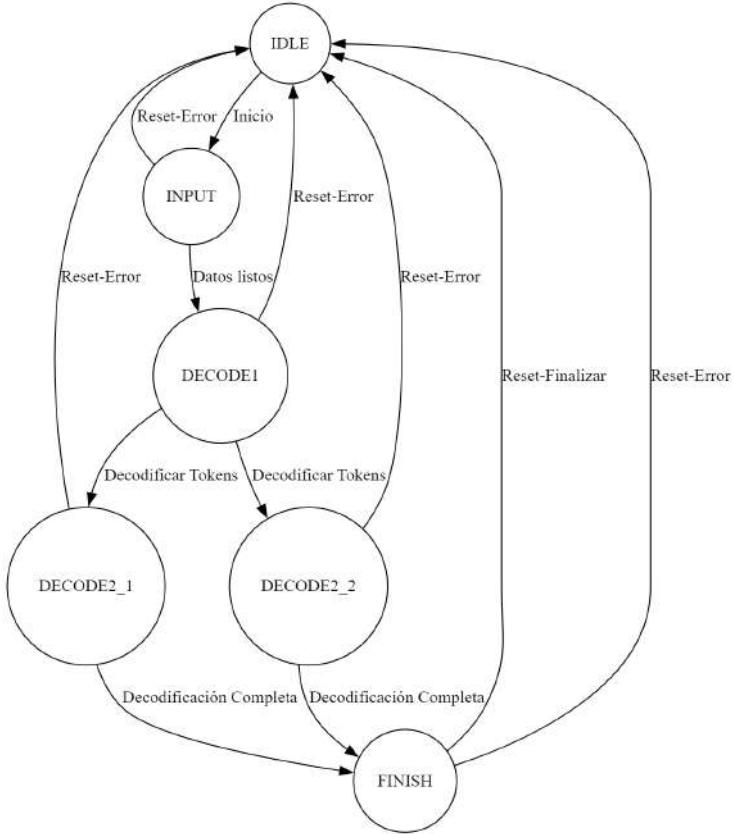

| 3.13 | Maquina de estados base de descompresor, elaboración propia. . . . .                       | 49 |

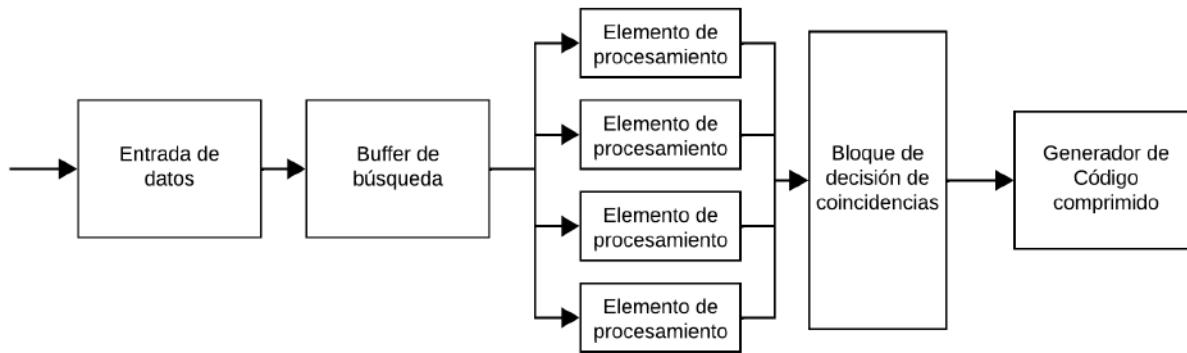

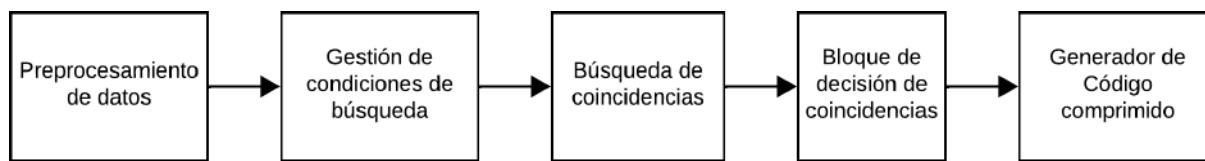

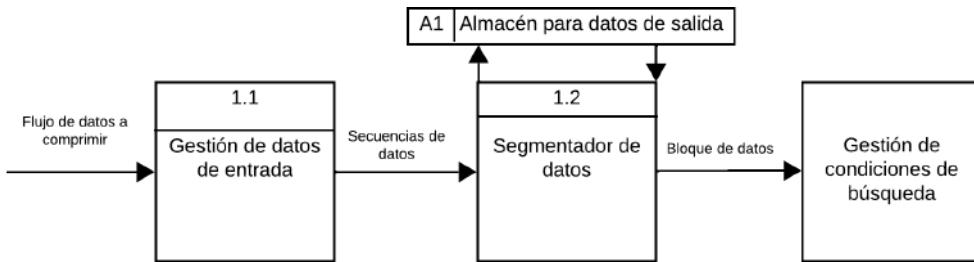

| 3.14 | Diagrama de bloques de arquitectura inicial, elaboración propia. . . . .                   | 50 |

| 3.15 | Diagrama de bloques de arquitectura corregido, elaboración propia. . . . .                 | 50 |

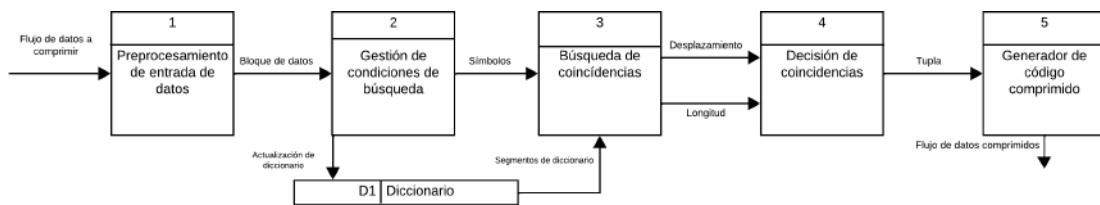

| 4.1  | Diagrama de arquitectura propuesta, elaboración propia. . . . .                            | 53 |

| 4.2  | Diagrama de módulo de preprocessamiento, elaboración propia. . . . .                       | 57 |

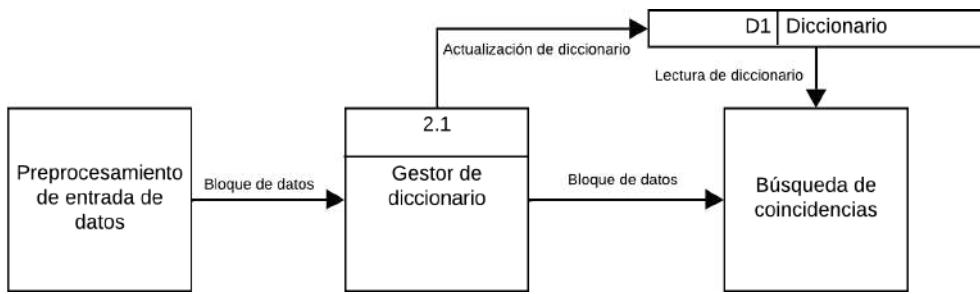

| 4.3  | Diagrama de módulo de gestión de condiciones de búsqueda, elaboración propia. . . . .      | 58 |

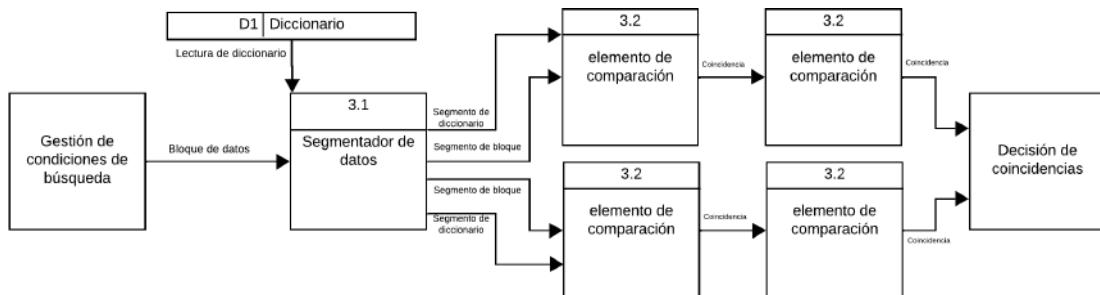

| 4.4  | Diagrama de módulo de búsqueda de coincidencias, elaboración propia. . . . .               | 59 |

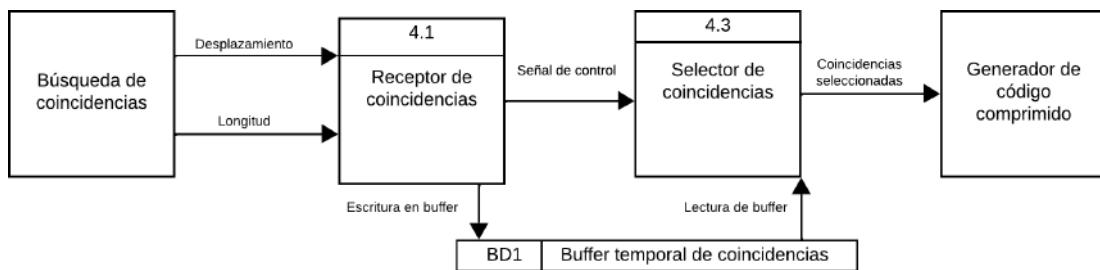

| 4.5  | Diagrama de módulo de decisión de coincidencias, elaboración propia. . . . .               | 61 |

| 4.6  | Diagrama de módulo de generador de código comprimido, elaboración propia. . . . .          | 62 |

| 5.1  | Diseño RTL de elemento de procesamiento, elaboración propia. . . . .                       | 66 |

| 5.2  | Matriz sistólica de la arquitectura, elaboración propia. . . . .                           | 66 |

| 6.1  | Diagrama de funcionamiento PLL, elaboración propia. . . . .                                | 77 |

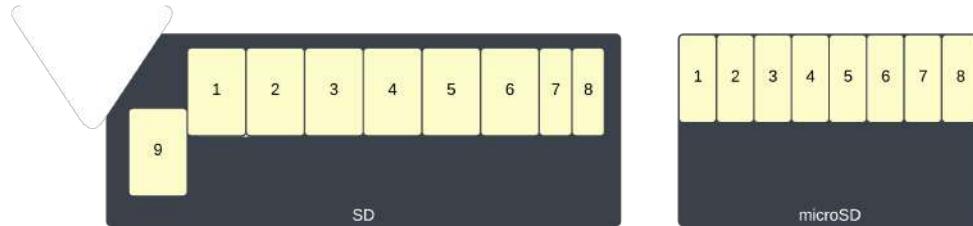

| 6.2  | Definición de pines SPI para tarjeta SD (izquierda) y SD (derecha), basado en [3]. . . . . | 77 |

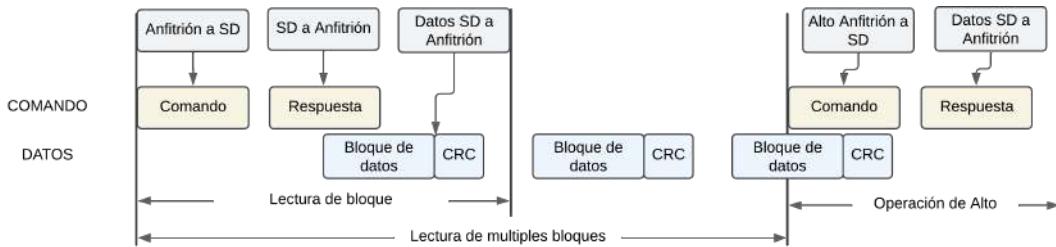

| 6.3  | Escritura de múltiples bloques hacia tarjeta SD, basado en [4]. . . . .                    | 79 |

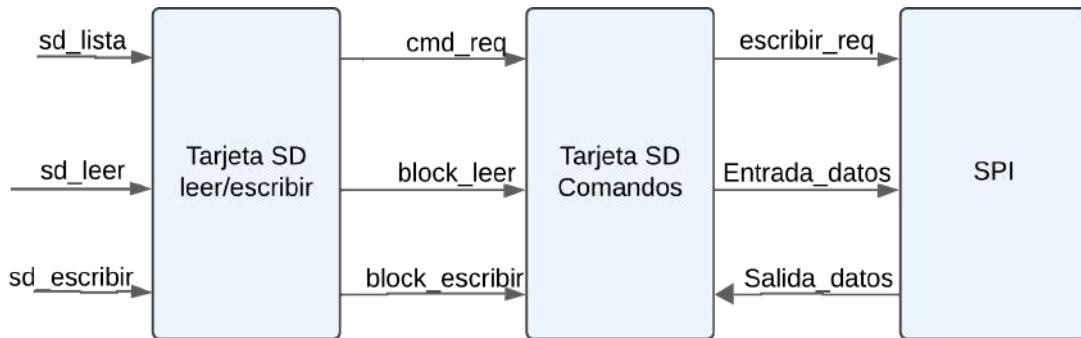

| 6.4  | Arquitectura para manejar tarjeta SD, basado en [4]. . . . .                               | 79 |

|     |                                                                                                           |     |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

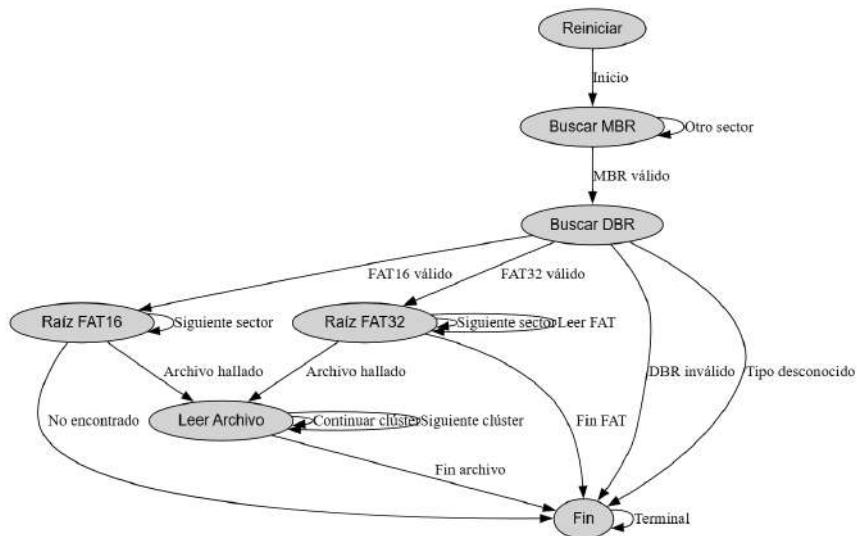

| 6.5 | Maquina finita de estados para manejar tarjeta SD, elaboración propia. . . . .                            | 81  |

| 6.6 | Acceso a SD correcto, elaboración propia. . . . .                                                         | 83  |

| 6.7 | Consumo energético de arquitectura propuesta, elaboración propia. . . . .                                 | 89  |

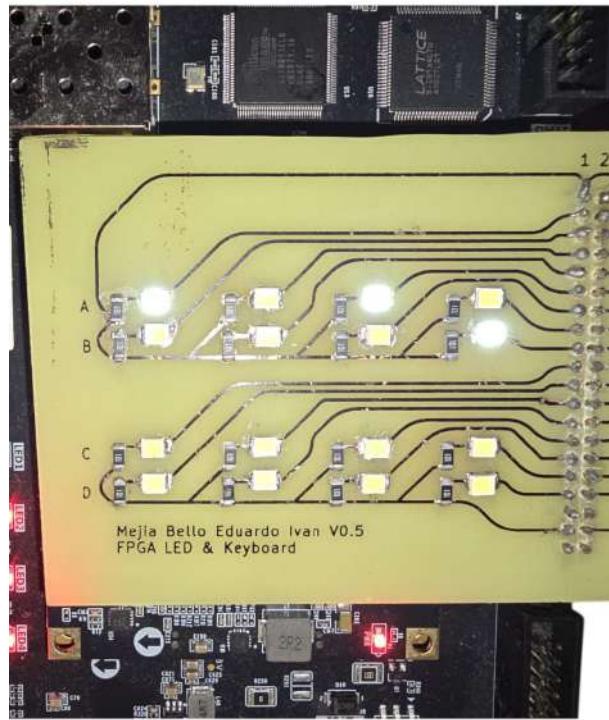

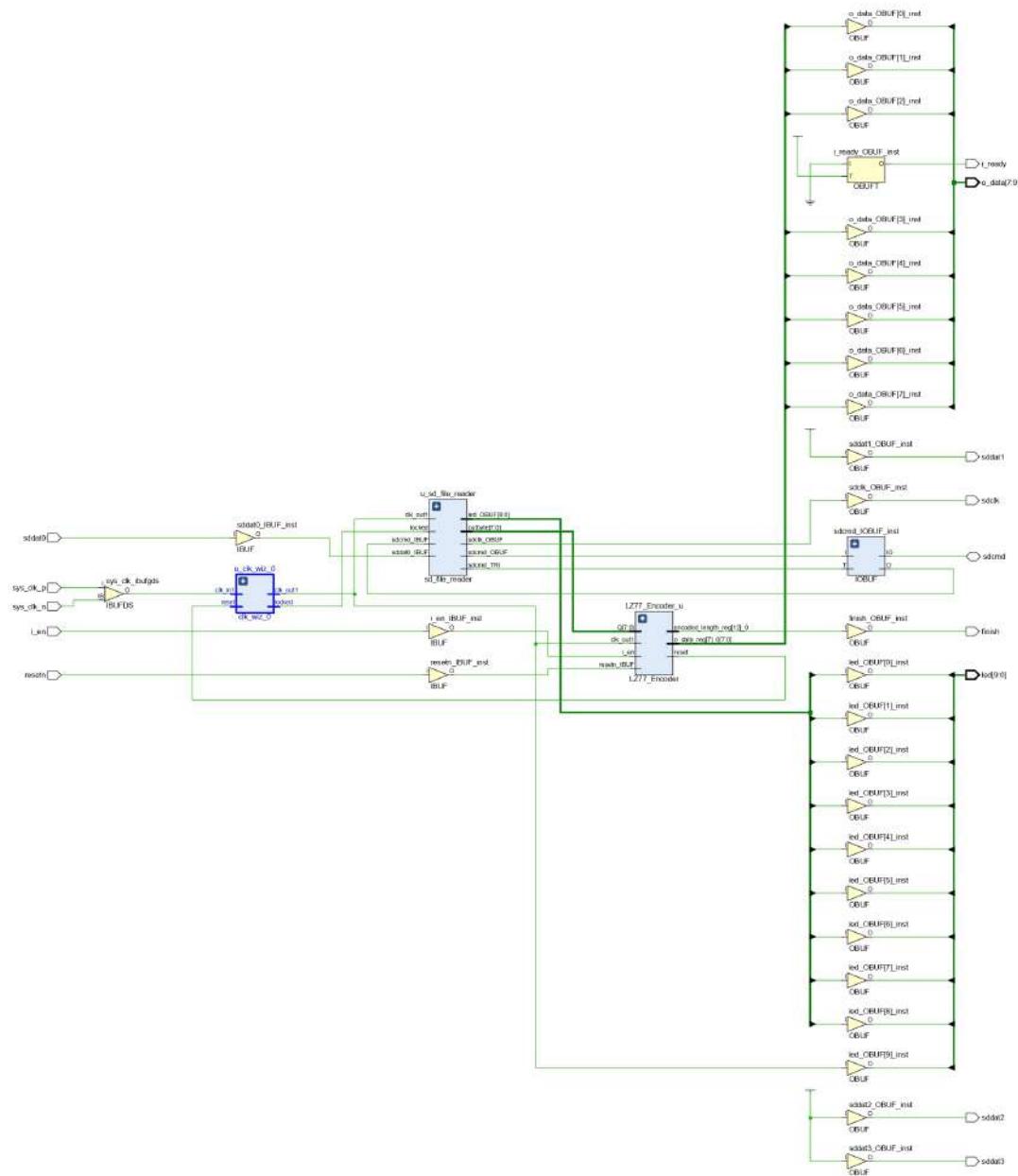

| A.1 | Esquemático de diseño de arquitectura propuesta con entrada desde tarjeta SD, elaboración propia. . . . . | 103 |

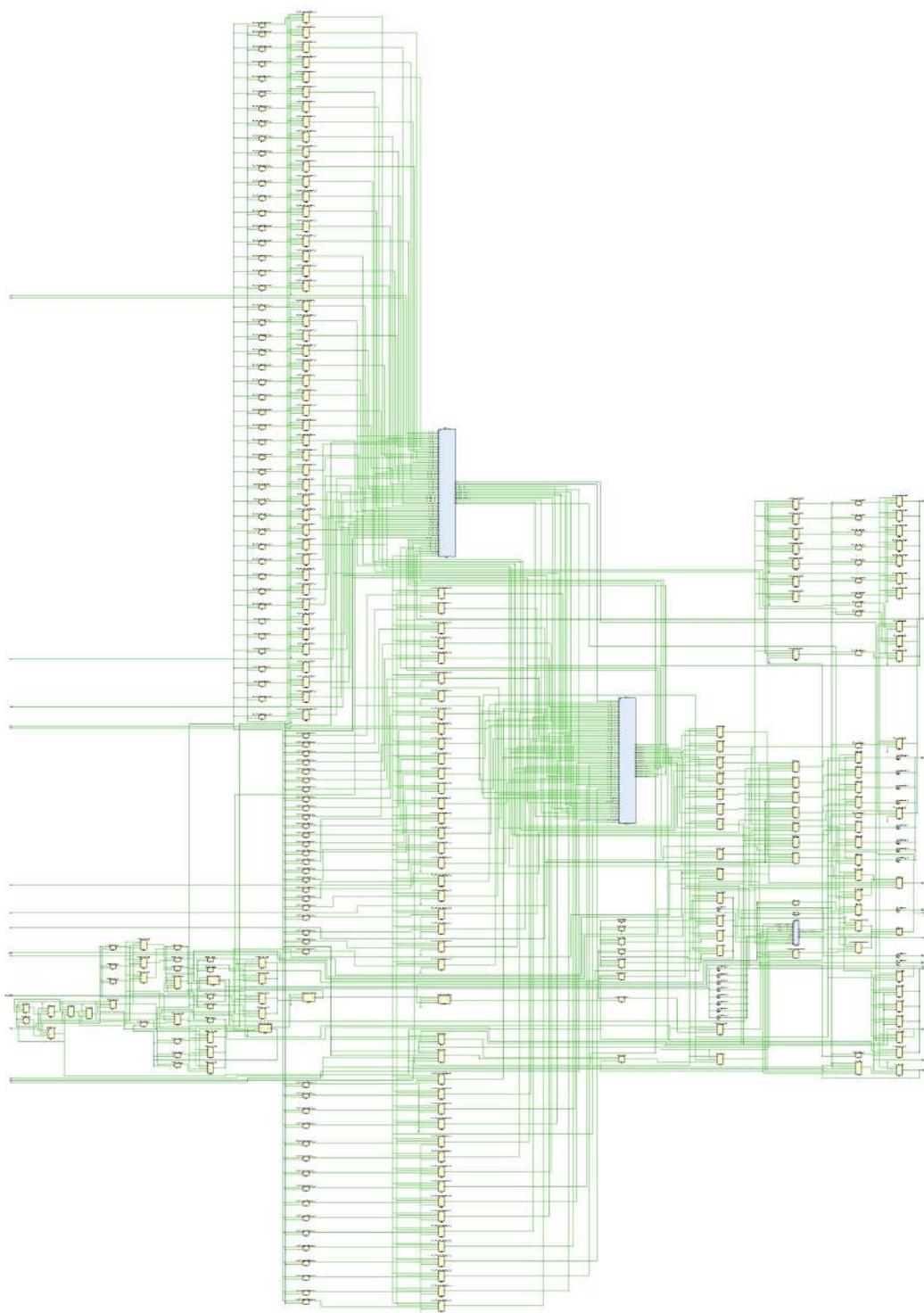

| A.2 | Esquemático de diseño de arquitectura propuesta, elaboración propia. . . . .                              | 104 |

# Indice de tablas

|      |                                                                                                       |    |

|------|-------------------------------------------------------------------------------------------------------|----|

| 1.1  | Comparación de velocidad de dispositivos móviles y procesadores, adaptado de [5] . . . . .            | 3  |

| 1.2  | Cronograma - 2 semestre (B2024), elaboración propia. . . . .                                          | 8  |

| 1.3  | Cronograma - 3 semestre (A2025), elaboración propia. . . . .                                          | 8  |

| 1.4  | Cronograma - 4 semestre (B2025), elaboración propia. . . . .                                          | 8  |

| 1.5  | Comparación de algoritmos de compresión, tomado de [6]. . . . .                                       | 10 |

| 2.1  | Comparación entre compresión sin pérdida y con pérdida, elaboración propia. . . . .                   | 16 |

| 3.1  | Valores ASCII de los caracteres de ejemplo, elaboración propia. . . . .                               | 41 |

| 3.2  | Decisión con seis símbolos, elaboración propia. . . . .                                               | 43 |

| 3.3  | Entrada completa, elaboración propia. . . . .                                                         | 44 |

| 3.4  | Entrada completa con diccionario dinámico pequeño, elaboración propia. . . . .                        | 45 |

| 4.1  | Segmentos en los que se divide el diccionario, elaboración propia. . . . .                            | 54 |

| 4.2  | Entradas y salidas de los módulos, elaboración propia. . . . .                                        | 63 |

| 6.1  | Resumen de rendimiento y consumo en Samsung S24 Ultra, basado en [7].                                 | 71 |

| 6.2  | Comparación Calgary Corpus en simulación, elaboración propia. . . . .                                 | 73 |

| 6.3  | Comparación Canterbury Corpus en simulación, elaboración propia. . . . .                              | 74 |

| 6.4  | Comparación Silesia Corpus en simulación, elaboración propia. . . . .                                 | 75 |

| 6.5  | Modos de operación disponibles en tarjetas SD, basado en [8]. . . . .                                 | 79 |

| 6.6  | Comparación Calgary Corpus en tarjeta física, elaboración propia. . . . .                             | 85 |

| 6.7  | Comparación Canterbury Corpus en tarjeta física, elaboración propia. . . . .                          | 86 |

| 6.8  | Comparación Silesia Corpus en tarjeta física, elaboración propia. . . . .                             | 87 |

| 6.9  | Distribución de corriente por dominio de alimentación, elaboración propia.                            | 89 |

| 6.10 | Comparación del consumo energético entre simulación y medición física. . . . .                        | 91 |

| 6.11 | Comparación de rendimiento: Arquitectura propuesta vs. Samsung S24 Ultra, elaboración propia. . . . . | 91 |

# Capítulo 1

## Introducción

En la actualidad, el mundo se encuentra rodeado de dispositivos que generan datos digitales constantemente. Desde los teléfonos móviles hasta los automóviles, los electrodomésticos inteligentes o los equipos médicos, todos estos aparatos producen y procesan información a un ritmo impresionante. Sin embargo, muchos de ellos enfrentan limitaciones como el espacio, el peso y el consumo energético, lo que hace que no siempre sea práctico usar procesadores genéricos diseñados para todo tipo de tareas. En este contexto, las soluciones de hardware dedicado están ganando protagonismo. Por ejemplo, un refrigerador puede usar sensores específicos para medir el nivel de agua o un automóvil puede depender de componentes dedicados para gestionar su sistema de frenos. Estas soluciones no solo mejoran el rendimiento, sino que optimizan los recursos disponibles, lo cual es clave en dispositivos pequeños y de bajo consumo. Lo más interesante es que estas tecnologías no están limitadas a laboratorios o proyectos de alta tecnología. Muchas de las cosas que se usan a diario ya dependen de microcontroladores y otros componentes dedicados para tareas como encender una pantalla, controlar un robot en una fábrica o monitorear signos vitales en un hospital.

El presente trabajo explora una arquitectura de hardware basada en la teoría de matrices sistólicas, que ofrece una combinación eficiente de potencia de procesamiento y flexibilidad. Estas arquitecturas son especialmente útiles en tareas repetitivas como la búsqueda y comparación realizada en la compresión de datos digitales, donde se busca reducir el espacio que ocupan los archivos sin perder información importante. Un ejemplo práctico sería un teléfono móvil que almacena más fotos o videos sin sacrificar espacio, gracias a que usa hardware diseñado para comprimir y descomprimir datos de manera rápida y eficiente. A lo largo de la historia se han propuesto y utilizado ampliamente muchas técnicas de compresión de datos sin pérdidas, por ejemplo, el código Huffman [9], código aritmético [10] y algoritmos de Lempel-Ziv (LZ) [11]. Diferentes arquitecturas de hardware, incluida la memoria de contenido direccionable [12], matriz sistólica [13], entre otras, se han propuesto. Con ello se han presentado varias realizaciones de hardware de LZ y sus variantes. Algunas hasta han sido patentadas [14].

Para las pruebas del diseño propuesto se utiliza una plataforma FPGA, que es un dispositivo reconfigurable. Esto permite probar y ajustar el diseño de hardware sin necesidad de fabricarlo desde cero, reduciendo costos y acelerando el desarrollo. Motivado por llegar a ser integrado en dispositivos móviles a futuro, para hacerlos más eficientes y capaces.

En un mundo donde cada byte de información cuenta, esta propuesta representa un paso importante para afrontar los retos del presente y colaborar en el futuro. Con tecnologías como esta, se abre la posibilidad de transformar no solo los dispositivos actuales, sino también la forma en que se maneja la enorme cantidad de datos producidos.

## 1.1. Planteamiento del problema

En la era actual, el acceso y la generación de información digital han alcanzado niveles sin precedentes gracias al avance de tecnologías como el Internet, los dispositivos móviles, las redes sociales, la domótica e incluso los propios sistemas operativos que utilizan estos dispositivos. Este ecosistema ha provocado un incremento exponencial en la cantidad de datos digitales generados (en adelante, simplemente "datos"), que deben ser transmitidos entre dispositivos y almacenados para su consulta o uso futuro. Estudios recientes revelan que el 90 % de los datos actuales han sido generados en los últimos dos años. En 2023, la generación global de datos alcanzó los 120 zettabytes y se espera que en 2025 ascienda a 181 zettabytes [15]. [16, 17] Este crecimiento plantea desafíos importantes, especialmente en países como México, que, tomando de ejemplo, se tienen 172 centros de datos, ocupando el puesto 12 en generación de datos a nivel mundial, por delante de países como India (152) y España (143). Respecto a los dispositivos celulares, de acuerdo con INEGI [18, 19] en el mismo periodo, 97.2 millones de personas usaban un teléfono celular en México, representando el 97.1 % de personas que se conectan a Internet. A pesar de este panorama, la infraestructura de conectividad presenta limitaciones significativas: en 2023, la velocidad promedio de descarga en México fue de 60.28 Mbps para conexiones de banda ancha fija y de 25.26 Mbps para datos móviles, ubicándose en los puestos 69 y 80 a nivel global, respectivamente [20, 21]. El almacenamiento y la transmisión de datos, tanto a nivel global como en México, enfrentan un aumento constante en la demanda, superando la capacidad promedio de transmisión disponible. Esta disparidad se agrava en los dispositivos móviles, que deben balancear limitaciones de tamaño, peso, consumo energético, poder de cómputo, entre otros. Estas características que se debe tener en cuenta al diseñar con orientación a los dispositivos móviles, dificultan el manejo de datos mediante soluciones basadas únicamente en software, considerando la necesidad de tener enfoques más dedicados. [5] Actualmente, las estrategias para superar estas limitaciones incluyen, por un lado, la transferencia de operaciones intensivas a la nube mediante Internet, y, por otro, el uso de aceleradores de hardware diseñados específicamente para tareas particulares en dispositivos móviles. Entre estos extremos existen soluciones intermedias, como aceleradores de hardware programables, que ofrecen flexibilidad y eficiencia en diversas aplicaciones. El avance tecnológico impulsado por la Ley de Moore ha beneficiado de forma desigual a los dispositivos móviles y a los dispositivos fijos, dejando en evidencia las brechas de capacidad de procesamiento entre ambos (ver tabla 1.1), donde se observa que, aun comparando los celulares de gama alta contra el promedio de procesadores de uso doméstico, sigue existiendo una brecha entre las prestaciones que pueden ofrecer cada uno. Siendo los dispositivos móviles en la actualidad muy capaces en comparación con hace 20 años o tan solo 10 años, pero los usuarios también cada vez esperan un mayor desempeño contenido en un menor tamaño, por ejemplo, el reconocimiento de voz, o fotografías con gran cantidad de datos tomadas

en una fracción de segundo. Estos desafíos resaltan la necesidad de hardware específico y diseñado con las mejores técnicas posibles.

Tabla 1.1: Comparación de velocidad de dispositivos móviles y procesadores, adaptado de [5]

| Computadora típica     |                     | Dispositivo móvil típico |                     | Año  |

|------------------------|---------------------|--------------------------|---------------------|------|

| Procesador             | Velocidad           | Dispositivo              | Velocidad           |      |

| Intel Core 2 Duo E6600 | 4.8 GHz (2 cores)   | Apple iPhone             | 412 MHz             | 2007 |

| Intel Core i5-2500K    | 13.2 GHz (4 cores)  | Samsung Galaxy S2        | 2.4 GHz (2 cores)   | 2011 |

| Intel Core i5-3570K    | 13.6 GHz (4 cores)  | Samsung Galaxy S4        | 6.4 GHz (4 cores)   | 2013 |

| Intel Core i5-6600K    | 14 GHz (4 cores)    | Samsung Galaxy S7        | 7.5 GHz (4 cores)   | 2016 |

| AMD Ryzen 5 1600       | 38.4 GHz (12 cores) | Google Pixel 2           | 17.4 GHz (8 cores)  | 2017 |

| AMD Ryzen 5 3600       | 43.2 GHz (12 cores) | Samsung Galaxy S20       | 18.46 GHz (8 cores) | 2020 |

| AMD Ryzen 7 5700X      | 54.4 GHz (16 cores) | Samsung Galaxy S24 Ultra | 22.89 GHz (8 cores) | 2024 |

En investigaciones realizadas, se ha demostrado que los circuitos integrados de aplicación especifican (ASIC) pueden ayudar a contrarrestar las limitaciones presentes en los dispositivos móviles [22], logrando tareas como la inferencia en el aprendizaje profundo [23] o la superresolución de imágenes [24]. Estos avances demuestran el potencial del diseño de hardware enfocado en problemas específicos.

Dado el aumento en la generación de datos y las limitaciones de conectividad y almacenamiento, es necesario tener en cuenta soluciones más eficientes. Este trabajo se centra en el diseño de una propuesta de compresión de datos en hardware, con el objetivo de ayudar a mitigar el uso del ancho de banda y almacenamiento en la actualidad y ser parte de la base de soluciones utilizadas en el futuro. Se busca generar una solución mediante hardware específico en compresión de datos para mejorar el uso de los recursos limitados disponibles.

### 1.1.1. Pregunta de investigación

¿Cómo se puede mejorar la utilización de hardware dedicado para comprimir archivos de texto sin pérdida?

### 1.1.2. Propuesta de solución

El incremento en la generación de datos requiere estrategias que combinen eficiencia y rendimiento. Para abordar esta problemática, se propone una arquitectura de hardware de compresión sin pérdida basada en el algoritmo LZ77, utilizando matrices sistólicas y presentada en un dispositivo de desarrollo de hardware (FPGA). Esta solución busca aprovechar en lo posible de mejor forma los recursos disponibles, con la motivación que en el futuro pueda llegar a ser implementado en dispositivos móviles, liberando al procesador principal de tareas intensivas de compresión y descompresión. A continuación, se detalla brevemente los aspectos clave de la propuesta a desarrollar.

#### 1. Estrategia de compresión

- a) Algoritmo base: LZ77 se seleccionó por su forma de funcionamiento, identificando patrones en los datos para reducir el tamaño de la información eliminando la

redundancia, todo ello sin perder información en el proceso. Su implementación en hardware permite paralelismo a nivel de bits.

- b) Implementación en matrices sistólicas: Generan una estructura eficiente para la implementación del algoritmo basado en LZ77. Cada celda en la matriz se diseña para realizar operaciones de comparación y desplazamiento de patrones, Se busca optimizar la búsqueda y comparación de los datos.

## 2. Arquitectura de hardware

- a) Unidad de compresión: Diseñada como un módulo específico dentro del FPGA, se encarga de aplicar el algoritmo LZ77 mediante una configuración paralela.

- b) Procesamiento en paralelo: El diseño utiliza una matriz sistólica para procesar el texto, para maximizar el rendimiento y reducir la latencia.

- c) Gestión de memoria: Se utilizan buffers para manejar segmentos de datos y disminuir el acceso a memoria externa, mejorando la eficiencia energética y reduciendo los tiempos de espera.

## 3. Tarjeta de desarrollo

- a) Se selecciona un FPGA por su flexibilidad y capacidad de re-configuración para realizar pruebas del diseño, sin requerir la fabricación y los recursos que ello conlleva. El diseño inicial utiliza hardware de pruebas compatible con lenguajes de descripción de hardware (VHDL/Verilog).

- a) Ventajas: Flexibilidad para ajustar el diseño y corregirlo, escalable y se puede configurar de formas diferentes, posibilidad de reutilizar bloques en futuros diseños.

## 4. Estrategia de validación

- a) Simulación y verificación: Se utilizarán herramientas específicamente desarrolladas para diseño de hardware, en este caso Vivado de AMD para sintetizar el diseño y simular su comportamiento frente a diferentes entradas de datos.

- b) Rendimiento: Comparación de rendimiento entre soluciones de software y la implementación en hardware. Se busca validar una mejora en la velocidad de compresión entre el 20 % y 47 % [25].

- c) Métricas de evaluación:

- 1) Latencia: Tiempo empleado en comprimir bloques de datos.

- 2) Eficiencia Energética: Consumo energético comparado con soluciones puramente de software.

- 3) Rendimiento: Capacidad de procesar datos en paralelo y que tasas de compresión se alcanzaron.

## 1.2. Objetivos

### 1.2.1. Objetivo general

Diseñar una arquitectura de hardware especializada en compresión de texto sin pérdida, basada en LZ77, empleando matrices sistólicas.

### 1.2.2. Objetivos específicos

1. Analizar los algoritmos de compresión de texto, considerando sus limitaciones, beneficios, eficiencia y rendimiento.

2. Comparar y seleccionar una técnica para implementar la compresión de texto en hardware, contemplando la eficiencia, rendimiento y adaptabilidad.

3. Diseñar una arquitectura de hardware que integre los elementos necesarios para la configuración de una matriz sistólica, enfocada en compresión de texto sin pérdida.

4. Validar la arquitectura diseñada de compresión sin pérdida, comprobando tasa de compresión, tiempo de procesamiento y parámetros de energía.

## 1.3. Justificación

El crecimiento sostenido del volumen de datos digitales, impulsado por la accesibilidad a la creación, almacenamiento y comunicación mediante dispositivos móviles, las redes 5G, los dispositivos IoT (Internet of Things en inglés), redes sociales, inteligencia artificial (IA) y dispositivos autónomos, entre otros, han generado un incremento considerable en el número de dispositivos que aportan y transmiten datos [20], [21]. Este aumento de datos digitales conlleva un incremento en los costos, la complejidad y el consumo energético requerido para almacenar o transmitir los datos.

El incremento de datos digitales ha transformado las necesidades de infraestructura tecnológica. En México, las carencias respecto al ancho de banda y almacenamiento contrastan con el crecimiento exponencial en la generación de datos, que alcanzó los 120 zettabytes en 2023 y se proyecta a 181 zettabytes para 2025 a nivel mundial [15].

Estas cifras son evidencia de que la capacidad de transmisión y almacenamiento de datos no puede mantenerse al ritmo de la generación de información. Con ello, el diseño de hardware dedicado para compresión de datos surge como una solución, especialmente en dispositivos móviles, que son el principal medio de acceso a Internet, representando el 97.1 % de la población que se conecta a Internet en el país [18].

Se ha investigado ampliamente en el campo de la compresión de datos [25], [26]. Esta técnica busca reducir el tamaño de los datos, mejorando así la eficiencia del almacenamiento y reduciendo los requisitos de ancho de banda para la transmisión. De forma general se puede clasificar en dos grandes vertientes, compresión con o sin pérdida, dependiendo de los requisitos de integridad de los datos. La compresión con pérdida supone que se puede tolerar cierta degradación en los datos, como ocurre con los archivos de audio en formato

MP3, donde la disminución de calidad no es tan evidente para el oído humano. En contraste, la compresión sin pérdida se utiliza cuando es fundamental mantener la integridad de los datos, como en los archivos de texto, donde perder un solo carácter puede causar errores en la interpretación del contenido o incluso dejar ilegible el documento. También se debe tener claro que la vida diaria está rodeada de dispositivos de hardware dedicados y que de hecho son esenciales para las tareas comunes, por ejemplo, los microcontroladores que manejan la salida a pantalla de los televisores, la medición del nivel de agua en refrigeradores, la unidad de control del motor (ECU) en los autos, el control de robots en líneas de ensamblaje, dispositivos médicos y de seguridad, entre otros. Considerando solo hardware dedicado a compresión de datos, compañías como Microsoft, Broadcom, AMD, ARM o Cadence, están trabajando en ello [27]. La motivación del presente trabajo es llegar a ser utilizado en dispositivos móviles en el futuro, ya que tienen la penalización por su misma naturaleza en sus limitaciones de tamaño, peso, y consumo energético, lo cual se traduce en un poder computacional significativamente menor en comparación con dispositivos estáticos. [5] Aunque estrategias como el *offloading* a nubes o *cloudlets* han sido exitosas, la implementación de aceleradores de hardware en los propios dispositivos móviles, como ASICs (Application-Specific Integrated Circuits), ofrece diversas ventajas, incluyendo baja latencia, operación en condiciones desconectadas y eficiencia energética superior. No obstante, el diseño e implementación de dispositivos de hardware específicos tiene ciertas barreras que en soluciones por software no existen, los más destacables son los altos costos de desarrollo y la falta de flexibilidad para realizar múltiples aplicaciones o realizar mejoras o correcciones.

En México, la conectividad limitada y la velocidad promedio de descarga, que ocupa los puestos 69 y 80 a nivel mundial para banda ancha fija y datos móviles respectivamente [20, 21], amplifican la necesidad de soluciones locales para la compresión de datos. El desarrollo del diseño de la arquitectura de compresión se planea para reducir el volumen de datos que la información utiliza tanto para poderse transmitir como para almacenarse en los dispositivos y liberar recursos en el procesador principal para otras tareas menos repetitivas o con necesidad más inmediata.

Además, optar por investigación en hardware diseñado para tareas específicas, no solo considera las necesidades inmediatas, sino que posiciona a México como un participante activo en la creación de soluciones escalables y eficientes frente a los retos globales que la creciente generación de datos crea.

En este contexto, surge el interés por el desarrollo de diseño de hardware dedicado en la compresión sin pérdida, aunque, por el tiempo y recursos que requiere la puesta en marcha de un hardware de propósito específico, se utiliza una arquitectura intermedia para realizar pruebas del diseño propuesto.

El diseño de una arquitectura de hardware de compresión basada en algoritmos como LZ77, implementada en plataformas FPGA, representa un paso crucial hacia una gestión de datos más eficiente en dispositivos móviles. Esta propuesta no solo aborda los retos actuales, sino que sienta las bases para la evolución tecnológica en México, aprovechando las ventajas de los aceleradores de hardware para mejorar el rendimiento y disminuir el consumo energético en un entorno de creciente generación de datos en dispositivos móviles.

## 1.4. Metodología

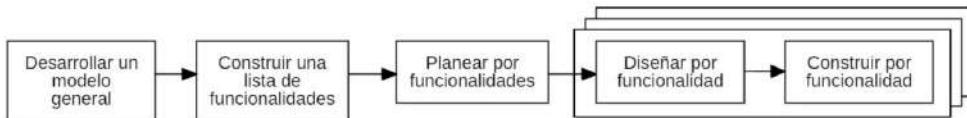

La metodología planeada para utilizarse a lo largo de este desarrollo principalmente es la basada en investigación teórica, ya que se centra en la creación y evaluación de teorías o modelos que describen y explican fenómenos en ciencias de la computación. En términos generales, se ha distinguido la teoría como lo opuesto a la práctica [28]. La investigación teórica, utiliza la forma de pensar e investigar en búsqueda de soluciones mediante la imaginación, abstracción, deducción; con ello desarrolla explicaciones o teorías sobre fenómenos. Se fundamenta en la corriente racionalista y es propia de las ciencias formales cuyos objetos de estudio son ideales o intangibles, como la matemática, lógica, física teórica o lingüística. Las técnicas incluyen la formulación de hipótesis, la construcción de modelos y la evaluación lógica. De esta forma se hará uso de lenguajes de diseño de hardware, específicamente de lenguajes de descripción de hardware, de los cuales se usan ampliamente VHDL y Verilog a nivel escolar e industrial. Teniendo en cuenta herramientas para analizar y corroborar los datos, como Vivado de AMD, el cual provee un entorno para diseño de tanto entradas como salidas, síntesis, lógica de las señales, verificación y simulación; siendo totalmente compatible con el hardware propuesto para la realización de este trabajo. Guiado por la metodología principal, se pretende utilizar para casos específicos en la prueba de concepto [29], [30], la metodología basada en funciones (Feature Driven Development) que ayuda a dimensionar y priorizar las actividades, dando prioridad a las funcionalidades más críticas. Consiste en cinco procesos, que proveen los métodos, técnicas y guías necesarias, los cuales se muestran en la siguiente figura.

Figura 1.1: Metodología basada en funciones, basado en (18).

La elección de estas metodologías se basa en el interés de estructurar el trabajo, ya que se realizará una investigación con enfoque a nivel teórico, de la cual se realizará una prueba de concepto en hardware, sustentada en teorías ya documentadas, así como desarrollar nuevo trabajo a partir de ellas, con la experimentación guiada con funciones puestas en marcha.

Como se puede apreciar, la metodología basada en funciones comienza con un modelo general que se va refinando proceso a proceso hasta llegar a su culminación. Parte de interés del uso específico de esta metodología recae en que las últimas dos fases son iterativas. Dando como resultado un mejor manejo de los pormenores que surjan en las fases que más trabajo requieren del sistema a desarrollar [30], [31], [32]. Para las etapas de representación de la arquitectura propuesta, por facilidad de comprensión se utilizan diagramas de bloques para visualización de las etapas por las que pasan las señales que representan la información procesada [33].

## 1.5. Cronograma

El cronograma se dividió por semestres, para una fácil lectura, se consideraron a grandes rasgos las actividades de mayor importancia para el diseño de la arquitectura de hardware, los apartados de investigación y el desarrollo de este. Se consideró el ajuste en lo posible con las vacaciones que hay entre ellos.

Tabla 1.2: Cronograma - 2 semestre (B2024), elaboración propia.

| Actividad                                   | Febrero | Marzo | Abril | Mayo | Junio |

|---------------------------------------------|---------|-------|-------|------|-------|

| Definición del tema y objetivos de la tesis |         |       |       |      |       |

| Revisión de literatura                      |         |       |       |      |       |

| Ánalisis comparativo                        |         |       |       |      |       |

| Familiarización con herramientas de diseño  |         |       |       |      |       |

| Redacción de tesis (Capítulo 1 y 2)         |         |       |       |      |       |

| Revisión con comité tutorial                |         |       |       |      |       |

Tabla 1.3: Cronograma - 3 semestre (A2025), elaboración propia.

| Actividad                       | Septiembre | Octubre | Noviembre | Diciembre | Enero |

|---------------------------------|------------|---------|-----------|-----------|-------|

| Diseño preliminar               |            |         |           |           |       |

| Diseño de arquitectura          |            |         |           |           |       |

| Integración de arquitectura     |            |         |           |           |       |

| Implementación en hardware      |            |         |           |           |       |

| Redacción de tesis (Capítulo 3) |            |         |           |           |       |

| Revisión con comité tutorial    |            |         |           |           |       |

Tabla 1.4: Cronograma - 4 semestre (B2025), elaboración propia.

| Actividad                             | Febrero | Marzo | Abril | Mayo | Junio |

|---------------------------------------|---------|-------|-------|------|-------|

| Simulación                            |         |       |       |      |       |

| Implementación del diseño en hardware |         |       |       |      |       |

| Desarrollo de la prueba de Concepto   |         |       |       |      |       |

| Optimización                          |         |       |       |      |       |

| Redacción de tesis                    |         |       |       |      |       |

| Revisión con comité tutorial          |         |       |       |      |       |

## 1.6. Estado del arte

En la actualidad, existe una amplia variedad de propuestas de compresión de datos, desarrolladas tanto por instituciones académicas como por grandes empresas tecnológicas, como Microsoft y Google. En particular, Google ha hecho público el trabajo realizado en el desarrollo de al menos cuatro algoritmos de compresión basados en el algoritmo LZ77. Uno de estos algoritmos es Snappy [34], el cual ha sido de código abierto desde 2011, y su versión más reciente (1.2.1) fue lanzada en mayo del año 2024. Snappy es una biblioteca

especializada en la compresión y descompresión de datos, no está diseñada con el objetivo de alcanzar la máxima compresión ni de ser compatible con otras bibliotecas de compresión, sino en lograr velocidades extremadamente altas con una compresión razonable. Comparada con el modo más rápido de Zlib, Snappy es aproximadamente diez veces más rápida en la mayoría de los casos, aunque los archivos comprimidos resultantes pueden ser entre un 20 % y un 100 % más grandes. Tomando en consideración el rendimiento, Snappy está diseñado para ser extremadamente rápido. En un solo núcleo de un procesador Core i7 en modo de 64 bits, puede comprimir datos a aproximadamente 250 MB/s o más, y descomprimirlos a alrededor de 500 MB/s o más (a modo de comparación, Zlib (Deflate) comprime a 74 MB/s en su configuración más rápida y a 24 MB/s con la configuración predeterminada). Estos valores corresponden a las entradas más lentas en su conjunto de pruebas, aunque este aumento de velocidad se logra a expensas de la relación de compresión, ya que la relación de compresión de Snappy es entre un 20 % y un 100 % menor que la de Zlib. En sus evaluaciones, Snappy supera en velocidad a otros algoritmos de compresión similares (como LZO, LZF, QuickLZ, etc.), manteniendo tasas de compresión comparables. Las tasas de compresión típicas, basadas en su conjunto de pruebas, son aproximadamente 1.5 a 1.7 veces para texto sin formato, de 2 a 4 veces para HTML, y 1.0 vez para archivos JPEG, PNG y otros datos ya comprimidos. En comparación, Zlib en su modo más rápido ofrece tasas de 2.6-2.8x, 3-7x y 1.0x respectivamente. Algoritmos más avanzados pueden alcanzar tasas de compresión superiores, aunque generalmente a costa de una menor velocidad. Es importante destacar que la relación de compresión puede variar significativamente según el tipo de datos de entrada. Aunque Snappy es bastante portátil, está optimizado principalmente para procesadores x86 de 64 bits y puede rendir de manera menos eficiente en otros entornos y los algoritmos de compresión rápida como Snappy son tan rápidos que las operaciones de E/S pueden ser el cuello de botella del algoritmo. Una de las ventajas inherentes de utilizar matrices sistólicas en el proyecto a desarrollar. El segundo algoritmo desarrollado por Google es nombrado Gipfeli [35], el cual es un algoritmo de compresión de alta velocidad que utiliza referencias hacia atrás con una ventana deslizante de 16 bits. Está basado en el trabajo de Lempel y Ziv de 1977, y se ha mejorado con una codificación de entropía *ad-hoc* tanto para literales como para referencias hacia atrás. Esta implementado en C++, en palabras de sus desarrolladores, esta optimizado para lograr un rendimiento excepcionalmente alto, aunque es aproximadamente un 30 % más lento que Snappy, pero logra un 30 % más de relación de compresión. La tasa de compresión que ofrece es comparable a la de Zlib en su modo más rápido, pero Gipfeli es aproximadamente tres veces más rápido. Esto lo convierte en una solución ideal para numerosos sistemas con limitaciones de ancho de banda, almacenamiento temporal de datos y procesamiento paralelo. Respecto al tercer algoritmo desarrollado por Google, es conocido como Zopfli [36]. El propósito de Zopfli es comprimir datos en el formato Deflate (basado en LZ77 parcialmente) con una eficiencia superior a la de implementaciones tradicionales como gzip y Zlib. Concretamente, Zopfli logra generar archivos comprimidos entre un 3.7 % y un 8.3 % más pequeños en comparación con gzip utilizando la opción `-best`. Sin embargo, el tiempo requerido para su ejecución es significativamente mayor, siendo aproximadamente cien veces más lento que gzip. Ya que el formato de datos que espera y general el algoritmo LZ77 es muy utilizado en la industria, también los datos comprimidos con Zopfli se pueden integrar en las aplicaciones sin problemas de compatibilidad. Un uso destacado de Zopfli

se encuentra en la web, donde se pueden comprimir las páginas estáticas, y el navegador al momento de visualizarlas las descomprime. Aunque la mejora en los tiempos de carga para el usuario final puede pasar desapercibida, en los dispositivos móviles, estas optimizaciones pueden notarse al tener un menor consumo energético. Otro uso que puede tener Zopfli es en las imágenes PNG, ya que también utilizan el algoritmo LZ77, lo cual se traduce en ahorros significativos en la transmisión de datos, dado el gran uso de PNG en la web. Sin embargo, debido a su bajo rendimiento en términos de velocidad, Zopfli podría no ser adecuado para la compresión de contenido personalizado. Respecto al último algoritmo de Google, es llamado Brotli [37], fue lanzado en 2015 y su última versión publicada fue la 1.1.0 en agosto de 2023. A diferencia de su predecesor Zopfli, Brotli no está diseñado para ser compatible con el algoritmo LZ77. En lugar de eso, Brotli aspira a ser un reemplazo moderno para LZ77. Dado que LZ77 es conocido por su rapidez tanto en la compresión como en la descompresión, además de su razonable relación de compresión, Brotli debe igualar o superar estas características para ser considerado un sustituto viable. Siendo un algoritmo de compresión sin pérdidas de propósito general que emplea una combinación de una variante moderna del algoritmo LZ77 y codificación Huffman. Esto le permite lograr una relación de compresión comparable a los métodos de compresión de propósito general más eficaces disponibles en la actualidad. Además, aunque su velocidad es similar a la de Deflate, Brotli ofrece una compresión significativamente más densa. Los cuatro algoritmos demuestran que en la práctica se sigue utilizando los algoritmos LZ, de forma pura o con variaciones de este, no solo porque tiene un soporte completo en los sistemas actuales, sino que es relativamente simple y rápido codificar y decodificar con él. Lo que da pie a realmente definir lo importante para tener en cuenta respecto a selección de algún algoritmo. Si considerar una variación de LZ, como LZ77 por ser el estándar en el cual se basan los demás algoritmos, o elegir alguna de las nuevas propuestas antes mencionadas. En [6] se comparó Brotli, Deflate incluido en la biblioteca Zlib, Zopfli, LZHAM, entre otros, limitando la selección de algoritmos a aquellos que generalmente tienen una tasa de compresión mayor que Deflate. Cabe aclarar que los resultados de las pruebas en su gran mayoría siempre dependen de las características del hardware sobre el cual se ejecutan, pero brindan la información suficiente para poder tener nociones de que parámetros se deben tener en consideración al momento de medir el rendimiento de la propuesta. Utilizando un set de datos estándar para poder corroborar y comprobar el funcionamiento de los compresores, en [6] utilizaron el corpus Canterbury [38], el cual contiene 1285 archivos con un total de 70,611,753 bytes. Considerando la velocidad de compresión y el nivel de compresión (la relación entre el peso del archivo original y el resultante), entre otras comparaciones que se pueden leer más a detalle en la referencia. La tabla 1.5 muestra los resultados de dicha comparación.

Tabla 1.5: Comparación de algoritmos de compresión, tomado de [6].

| Algoritmo | Nivel de compresión | Velocidad de compresión (Mb/s) | Velocidad de descompresión (Mb/s) |

|-----------|---------------------|--------------------------------|-----------------------------------|

| Deflate:1 | 2.913               | 93.5                           | 323                               |

| Deflate:9 | 3.371               | 15.5                           | 347.3                             |

| Brotli:1  | 3.381               | <b>98.3</b>                    | 334                               |

| Brotli:11 | <b>4.347</b>        | 0.5                            | 289.5                             |

| Zopfli    | 3.580               | 0.2                            | <b>342.1</b>                      |

Donde, como se mencionó antes, debido a que son algoritmos de software que dependen del hardware, los resultados son muy dependientes del ancho de banda del almacenamiento utilizado, el procesador, la memoria RAM, el sistema operativo, la cantidad de otros procesos ejecutándose, etc...., más aún, el artículo fue creado por Google, por lo tanto, es razonable entender que tiene cierta tendencia a hacer notar que el algoritmo Brotli ofrece mejores resultados que sus contrapartes. Los resultados de la tabla 1.5 dan la oportunidad de conocer el rendimiento promedio que tiene Deflate y sus contrapartes actuales funcionando en dispositivos anfitriones de 64 bits. Los cuales se aprecia que están limitados principalmente por el sistema operativo, ya que, al ser un sistema de propósito general, tiene que asignar el tiempo a diversas tareas, disminuyendo las prestaciones que puede ofrecer el algoritmo. Considerando la plataforma CUDA de NVIDIA, representa una vía clave para la realización de pruebas, gracias a la capacidad de sus GPUs para manejar tareas computacionales de alta demanda mediante programación paralela. Esta dependencia puede ser percibida como una ventaja o una desventaja, de acuerdo con las metas específicas de cada proyecto. CUDA ofrece un entorno con herramientas para administrar hilos y la memoria, lo que permite aprovechar el rendimiento de las GPUs en tareas paralelas. Tomando el ejemplo de CURC [39], el cual es un compresor de datos genómicos utilizando la GPY y CPU de forma heterogénea. CURC logra una compresión mayor que las herramientas tradicionales basadas exclusivamente en CPUs, como SPRING, debido a su capacidad para manejar tareas masivas de forma paralela con mayor velocidad y menor costo computacional. CURC ofrece una velocidad de compresión entre 2.76 y 6.54 veces mayor, y una velocidad de descompresión hasta 2.52 veces superior en comparación con otras herramientas tradicionales, sin sacrificar la tasa de compresión. Además, el sistema se puede escalar para soportar múltiples GPUs, pero tener en cuenta que deben de alinearse con la infraestructura que proporciona NVIDIA. Sin embargo, a pesar de estas ventajas, la dependencia en cuanto a CUDA y NVIDIA plantea varios problemas. La limitación más seria es la confianza total en una única compañía para el soporte de hardware, actualizaciones y todas las herramientas necesarias para el desarrollo. Este punto conllevará problemas si NVIDIA decide que el hardware utilizado se considera obsoleto o si la compañía toma decisiones que puedan afectar la continuidad de soporte o la disponibilidad del hardware. Así como el hecho de que el software solo puede ser accedido por las GPUs de NVIDIA con soporte de CUDA y únicamente la versión funcional y soportada para la GPU utilizada.

Por último, es importante señalar que CUDA es una tecnología propietaria, lo que excluye su uso en entornos que no pueden soportarla y dificulta la portabilidad hacia otras plataformas. Este factor puede limitar las opciones de expansión futura y restringir la flexibilidad del proyecto.

Se diseñará en lo posible el algoritmo en hardware, ya que brinda la oportunidad de que sea dedicado para una sola tarea, comprimir o descomprimir, dando pie a obtener mejores resultados que los ofrecidos solo por software. Involucrando la optimización de la arquitectura mediante matrices sistólicas, se busca afrontar el problema generado por el ancho de banda limitado y las capacidades limitadas que se tienen en los dispositivos móviles en la actualidad, siendo un sustento para contribuir a un futuro de desarrollo sin depender de tecnología de alguna compañía o técnica patentada. Involucrando al hardware, existen varios proyectos con orientación a utilizarlo para distintos fines en reemplazo de soluciones vía software, uno de los ellos [40], busca implementar Deflate en hardware, específicamente

en un FPGA, presentando algunos aspectos de su implementación de hardware para los codificadores LZ77 y Huffman, componentes clave del algoritmo Deflate. Con trabajo a futuro de una posible integración en sistemas de almacenamiento y comunicación de datos. Uno de los aspectos clave del algoritmo Deflate, es que brinda la opción de utilizar codificadores estáticos o dinámicos; estos últimos calculan las frecuencias en función de los datos de entrada; aquí es donde la mayoría de la literatura enfocada en soluciones vía hardware no cumplen con los requisitos para Deflate, ya que se ocupan solo de diseñar diccionarios estáticos. Con ello ofrece espacio para el presente trabajo y su incursión con diccionarios dinámicos. Orientado el desarrollo de hardware en la arquitectura utilizada, se puede buscar implementar el algoritmo Deflate de forma directa, pero esto no aprovecharía en lo posible los recursos que ofrece el FPGA, en [41] se analiza la implementación de hardware del algoritmo de compresión de datos Lempel-Ziv (LZ), enfatizando su importancia en las comunicaciones y el almacenamiento de datos de alta velocidad. Explora varias arquitecturas de hardware de compresión LZ, como la memoria direccionable de contenido (CAM), la matriz sistólica, y compara su eficiencia en términos de velocidad, costo de hardware y capacidad. Se introduce una nueva técnica paralela basada en matrices sistólicas para implementar el algoritmo LZ centrada en mejorar la latencia y la eficiencia. Además, incluye un análisis del efecto de la longitud del buffer de entrada en la relación de compresión y presenta una implementación FPGA de la técnica propuesta para la compresión y descompresión sobre la marcha. La implementación propuesta se describe como eficiente en área y velocidad. Da información sobre cómo seleccionar la longitud del búfer para una relación de compresión óptima, mostrando las implicaciones de la relación entre la longitud del búfer y la eficiencia de la compresión. Parte importante para este trabajo es que realiza una comparación de diseños de matrices sistólicas, ofreciendo los resultados de la implementación del diseño utilizando un FPGA de XILINX, lo que demuestra el potencial de mejoras significativas en la tasa de compresión y la eficiencia. Así como existe desarrollo en compresión vía software por parte de grandes compañías como Google, también se tiene interés en soluciones por hardware. Debido a que la compresión es algo esencial en la búsqueda del manejo de datos, considerando los niveles de generación de datos que se tiene actualmente. Existe documentación de un proyecto de 2019 [28], donde están involucrados diversas compañías como Intel, AMD, ARM, Broadcom, cadence, synopsys, entre otros. Creando una alianza para desarrollar un algoritmo de compresión, teniendo en cuenta la optimización y su implementación en hardware para los tipos de datos comunes en las cargas de trabajo de almacenamiento en la nube. Al introducir innovaciones a nivel de sistema, mencionan haber logrado alcanzar mayores niveles de compresión, mejor rendimiento y menor latencia en comparación con los algoritmos existentes. Microsoft es la principal compañía involucrada, la cual nombra al proyecto “Microsoft’s Project Zipline” y hace mención que los resultados tienen un nivel de compresión hasta 2 mayor en comparación con el modelo Zlib-L4 de 64 KB comúnmente utilizado. Mejoras como esta pueden generar beneficios directos en la administración de datos, tanto para las empresas como para los usuarios finales, teniendo un potencial ahorro de costos. Microsoft menciona que tiene un repositorio público, donde se puede tener acceso a especificaciones de diseño de hardware y código fuente de Verilog para lenguaje de transferencia de registros (RTL), donde literalmente mencionan “con contenido inicial disponible hoy y más próximamente”. Caso que lamentablemente desde esa primera y única publicación en 2019, no se tiene

más información actualizada del proyecto. Lo cual hace pensar en que el proyecto en la actualidad pudo haber pasado por, su abandono, debido a la alta especialización su privatización de este, entre otras posibles opciones. Dando pie a una interesante propuesta, que, en lo posible, dado el alcance del presente trabajo y los recursos disponibles, se toma en consideración los proyectos relacionados que en la actualidad otros investigadores realizan en torno a la compresión y la utilización de hardware en dicha tarea.

### 1.6.1. Compresión en dispositivos móviles

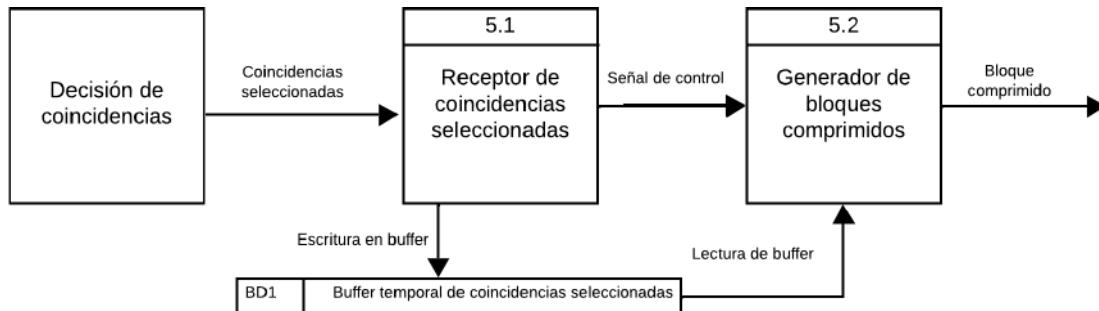

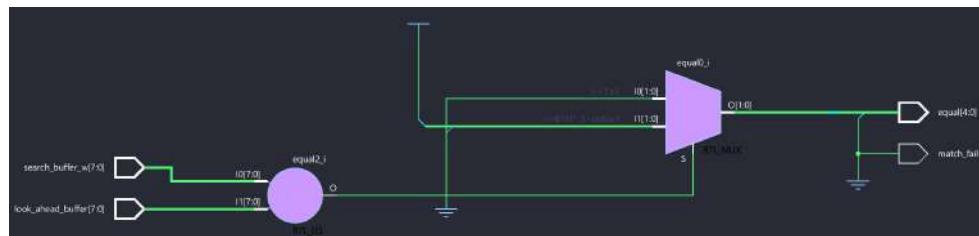

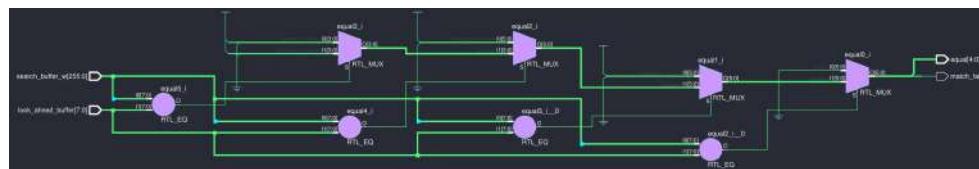

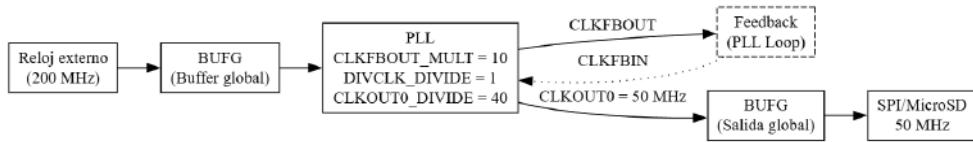

[42] Históricamente se ha tenido interés en desarrollar dispositivos móviles con interfaces inalámbricas que provean comunicación incluso mientras el usuario se mueve entre diversas ubicaciones, en otras palabras, el desarrollo de dispositivos que eliminan las restricciones de tiempo y espacio impuestas por las computadoras de escritorio y las redes cableadas. Donde la computación móvil a transformado la forma en que se tiene acceso continuo a servicios y recursos de redes terrestres. El desarrollo de estos dispositivos debe tener en cuenta aspectos como las comunicaciones inalámbricas, la movilidad y la portabilidad. El primer apartado, permite la conexión sin cables, pero enfrenta problemas como la latencia, desconexiones frecuentes y una menor capacidad de ancho de banda en comparación con las redes cableadas. En entornos donde se tenga que depender de dispositivos móviles las desconexiones son comunes debido a la interferencia, que a su vez hace variar el ancho de banda y que se generen complicaciones adicionales, por lo que se necesitan estrategias que puedan adaptarse a estas limitaciones. Considerando la portabilidad, el diseño de dispositivos móviles conlleva restricciones significativas en cuanto al tamaño, peso, consumo de energía y capacidad de almacenamiento. Minimizar el consumo de energía es crucial para prolongar la vida útil de la batería, mientras que la capacidad de almacenamiento limitada obliga a emplear soluciones como la compresión de archivos y el acceso remoto a datos. aunque la computación móvil ofrece la posibilidad de eliminar las restricciones de tiempo y lugar impuestas por los sistemas tradicionales, plantea desafíos únicos que requieren adaptar las estructuras y sistemas actuales para soportar esta nueva realidad. El uso masivo de dispositivos móviles con funciones avanzadas fue iniciado, entre otros, con los asistentes digitales (PDA por sus siglas en inglés), concebidos como dispositivos autocontenidos que eran parte mediante una red móvil de una infraestructura de cómputo mayor. Uno de sus enfoques era permitir el acceso continuo a servicios y recursos, esta combinación de movilidad y redes inalámbricas sentó las bases para nuevas aplicaciones y formas de interactuar, que incluso en fechas recientes tienen gran relevancia en variedad de áreas, gracias a diferentes dispositivos creados bajo los mismos principios, como los teléfonos inteligentes, dispositivos de Internet, tarjetas inteligentes, computadoras corporales, sensores de redes, etc... [43] La evolución tecnológica ha impulsado el desarrollo de procesadores más complejos, con un enfoque en la comunicación, rendimiento y bajo consumo de energía. En sus inicios, los teléfonos móviles de la primera generación (1G) usaban transmisión analógica, que requería más energía y admitía pocos usuarios. Con la llegada de la segunda generación (2G), se adoptaron los procesadores de señal digital (DSP), que proporcionaban una arquitectura flexible y rentable. A medida que avanzó la tecnología, arquitecturas más modernas como los procesadores VLIW y SIMD permitieron un mejor rendimiento y menor consumo de energía. Convirtiendo a los dispositivos móviles en